什麽是凸塊制(zhì)造(Bumping)技(jì)術(shù)

行(xíng)業資訊 | 2023-04-23 16:29

凸塊制(zhì)造技(jì)術(shù)是各類先進封裝技(jì)術(shù)得(de)以進一步發展演化的基礎,在集成電(diàn)路封裝中具有(yǒu)重要意義。倒裝(FC)、扇出型(Fan-out)封裝、扇入型(Fan-in)封裝、芯片級封裝(CSP)、三維立體(tǐ)封裝)(3D)、系統級封裝(SiP)等先進封裝結構與工藝實現的關鍵技(jì)術(shù)均涉及凸塊制(zhì)制(zhì)造技(jì)術(shù)。矽通(tōng)孔技(jì)術(shù)(TSV)、晶圓級封裝(WLP)、微電(diàn)子機械系統封裝(MEMS)等先進封裝結構與工藝均是凸塊制(zhì)造技(jì)術(shù)的演化和(hé)延伸。

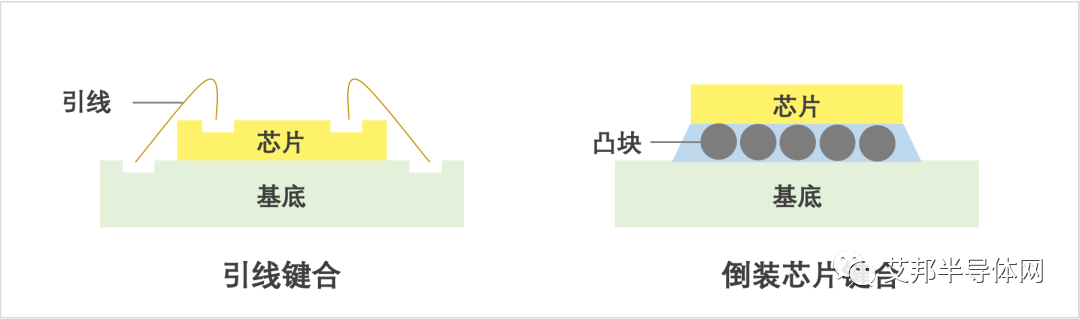

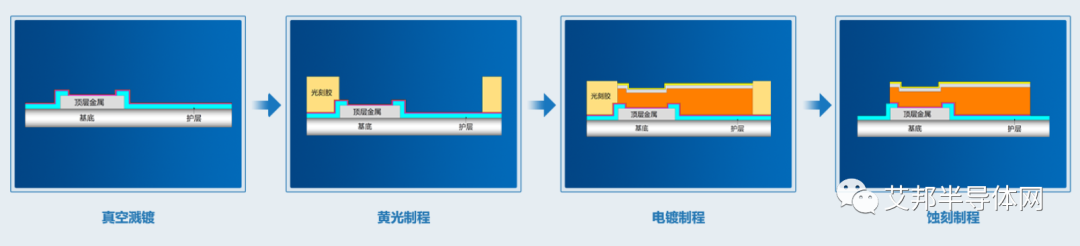

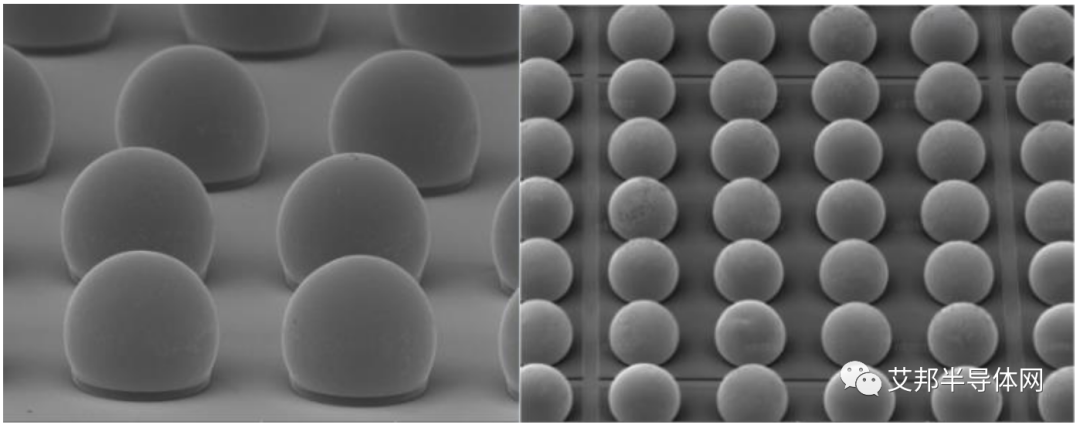

凸塊制(zhì)造技(jì)術(shù)(Bumping)是在芯片上(shàng)制(zhì)作(zuò)凸塊,通(tōng)過在芯片表面制(zhì)作(zuò)金屬凸塊提供芯片電(diàn)氣互連的“點”接口,廣泛應用于 FC、WLP、CSP、3D 等先進封裝。凸塊是定向生(shēng)長于芯片表面,與芯片焊盤直接相連或間(jiān)接相連的具有(yǒu)金屬導電(diàn)特性的凸起物。凸塊工藝介于産業鏈前道(dào)集成電(diàn)路制(zhì)造和(hé)後道(dào)封裝測試之間(jiān),是先進封裝的核心技(jì)術(shù)之一。凸塊制(zhì)造過程一般是基于定制(zhì)的光掩模,通(tōng)過真空(kōng)濺鍍、黃光、電(diàn)鍍、蝕刻等環節而成,該技(jì)術(shù)是晶圓制(zhì)造環節的延伸,也是實施倒裝(FC)封裝工藝的基礎及前提。相比以引線作(zuò)為(wèi)鍵合方式傳統的封裝,凸塊代替了原有(yǒu)的引線,實現了"以點代線"的突破。該技(jì)術(shù)可(kě)允許芯片擁有(yǒu)更高(gāo)的端口密度,縮短(duǎn)了信号傳輸路徑,減少(shǎo)了信号延遲,具備了更優良的熱傳導性及可(kě)靠性。此外,将晶圓重布線技(jì)術(shù)(RDL)和(hé)凸塊制(zhì)造技(jì)術(shù)相結合,可(kě)對原來(lái)設計(jì)的集成電(diàn)路線路接點位置(I/O Pad)進行(xíng)優化和(hé)調整,使集成電(diàn)路能适用于不同的封裝形式,封裝後芯片的電(diàn)性能可(kě)以明(míng)顯提高(gāo)。二、凸塊制(zhì)造技(jì)術(shù)演變及發展曆史

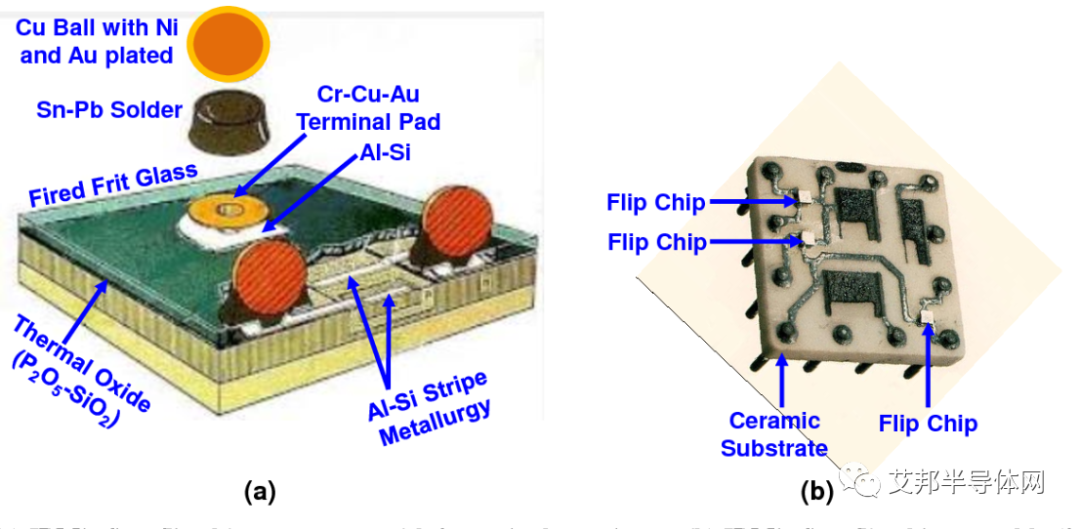

凸塊制(zhì)造技(jì)術(shù)起源于 IBM 在 20 世紀 60 年代開(kāi)發的 C4 工藝,即"可(kě)控坍塌芯片連接技(jì)術(shù)"(Controlled Collapse Chip Connection'),該技(jì)術(shù)使用金屬共熔凸點将芯片直接焊在基片的焊盤上(shàng),焊點提供了與基片的電(diàn)路和(hé)物理(lǐ)連接,該技(jì)術(shù)是集成電(diàn)路凸塊制(zhì)造技(jì)術(shù)的雛形,也是實現倒裝封裝技(jì)術(shù)的基礎,但(dàn)是由于在當時(shí)這種封裝方式成本極高(gāo),僅被用于高(gāo)端 IC 的封裝,因而限制(zhì)了該技(jì)術(shù)的廣泛使用。(a) IBM 的首個(gè)具有(yǒu) 3 個(gè)端子晶體(tǐ)管的倒裝芯片組件;(b) IBM 首個(gè)在陶瓷基闆上(shàng)的倒裝芯片組件(3 個(gè)芯片)C4 工藝在後續演化過程中逐漸被優化,如采用在芯片底部添加樹(shù)脂的方法,增強了封裝的可(kě)靠性。這種創新使得(de)低(dī)成本的有(yǒu)機基闆得(de)到了發展,促進了 FC 技(jì)術(shù)在集成電(diàn)路以及消費品電(diàn)子器(qì)件中以較低(dī)成本使用。此外,無鉛材料得(de)到了廣泛的研究及應用,凸塊制(zhì)造的材料種類不斷擴充。在 20 丗紀 80 年代到 21 世紀初,集成電(diàn)路産業由日本轉移至韓國、中國台灣,集成電(diàn)路細分領域的國際分工不斷深化,凸塊制(zhì)造技(jì)術(shù)也逐漸由蒸鍍工藝轉變為(wèi)濺鍍與電(diàn)鍍相結合的凸塊工藝,該工藝大(dà)幅縮小(xiǎo)了凸塊間(jiān)距,提高(gāo)了産品良率。近年來(lái),随着芯片集成度的提高(gāo),細節距(Fine Pitch)和(hé)極細節距(Ultra Fine Pitch)芯片的出現,促使凸塊制(zhì)造技(jì)術(shù)朝向高(gāo)密度、微間(jiān)距方向不斷發展。三、凸塊制(zhì)造的主要技(jì)術(shù)類别

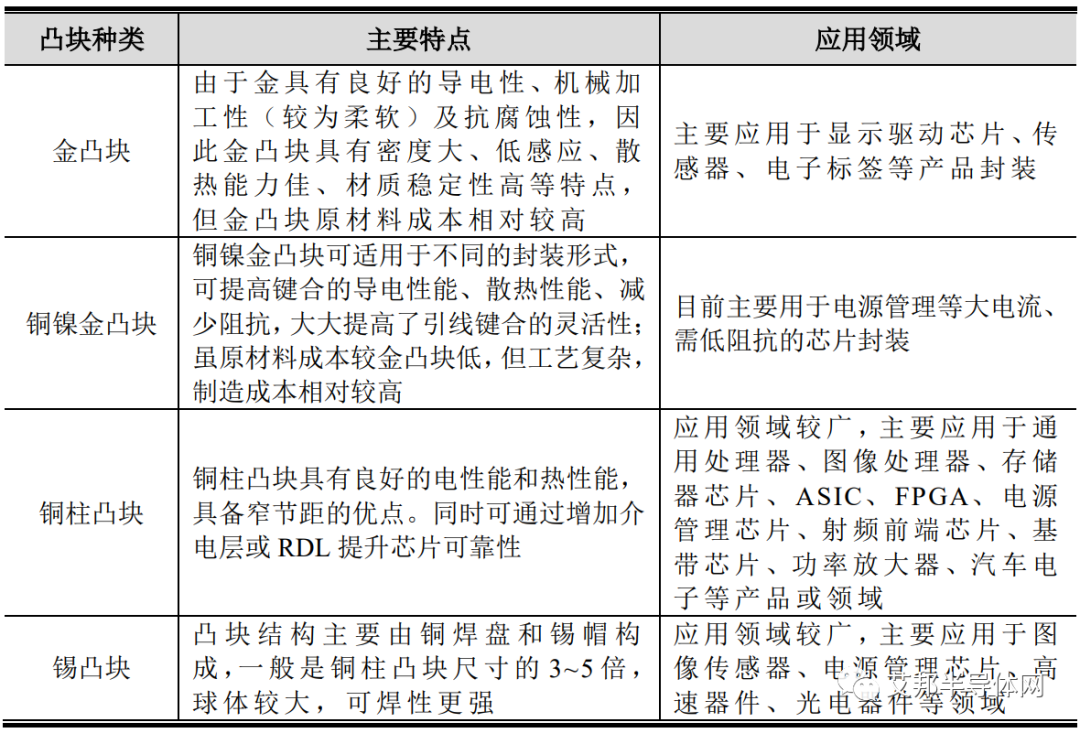

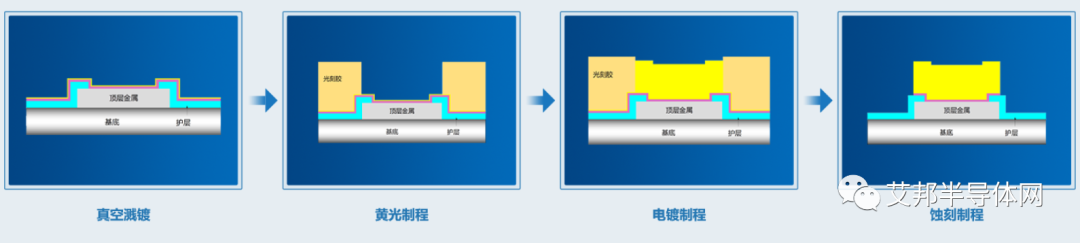

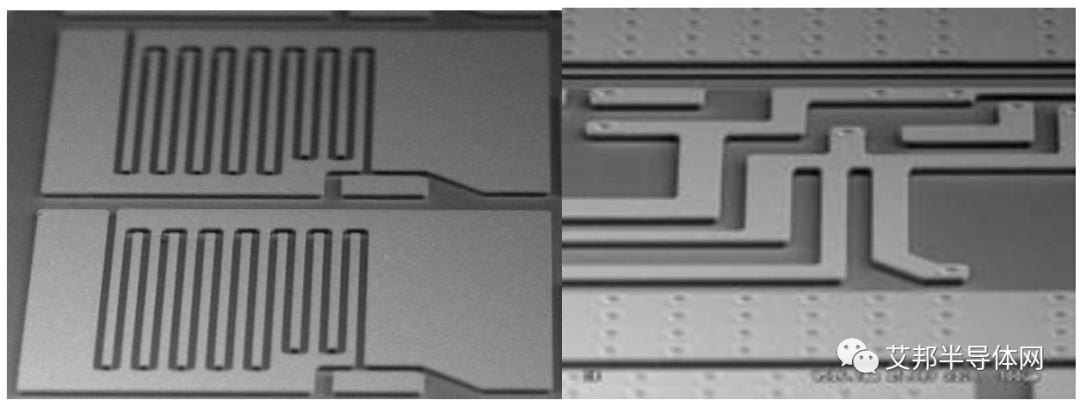

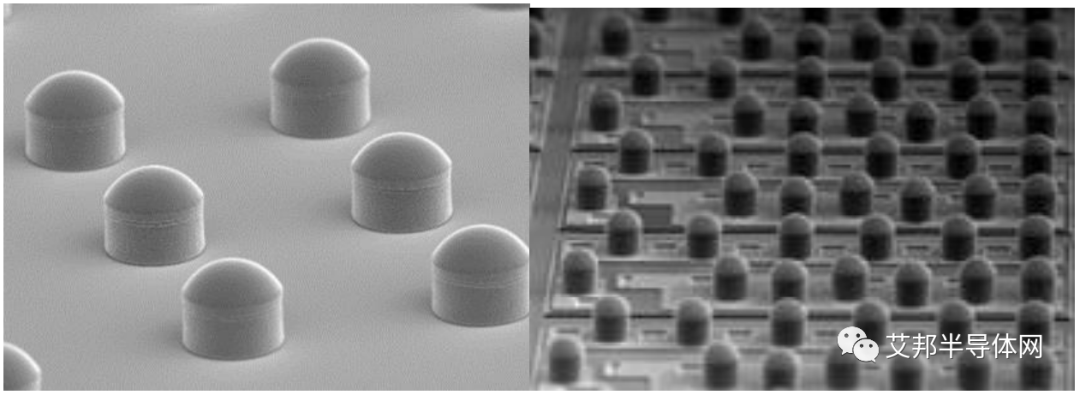

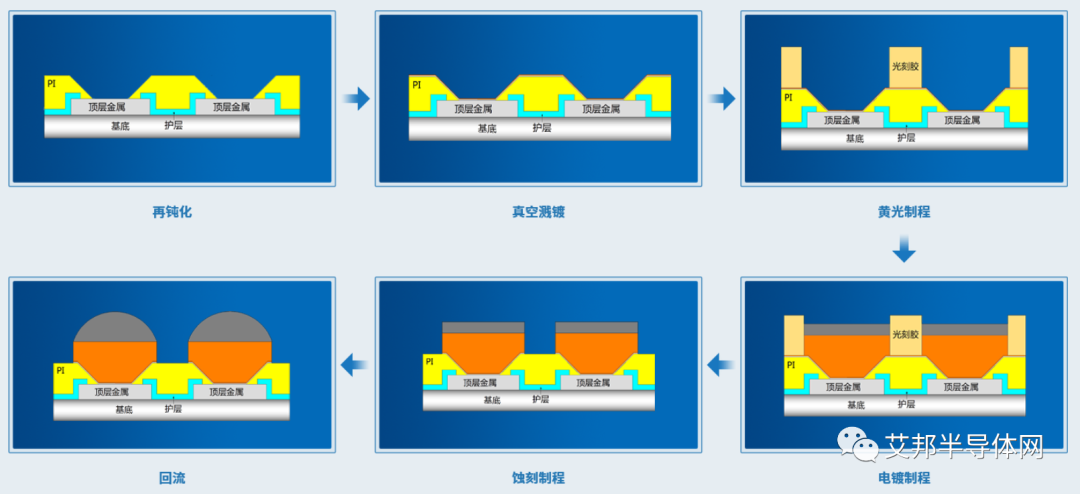

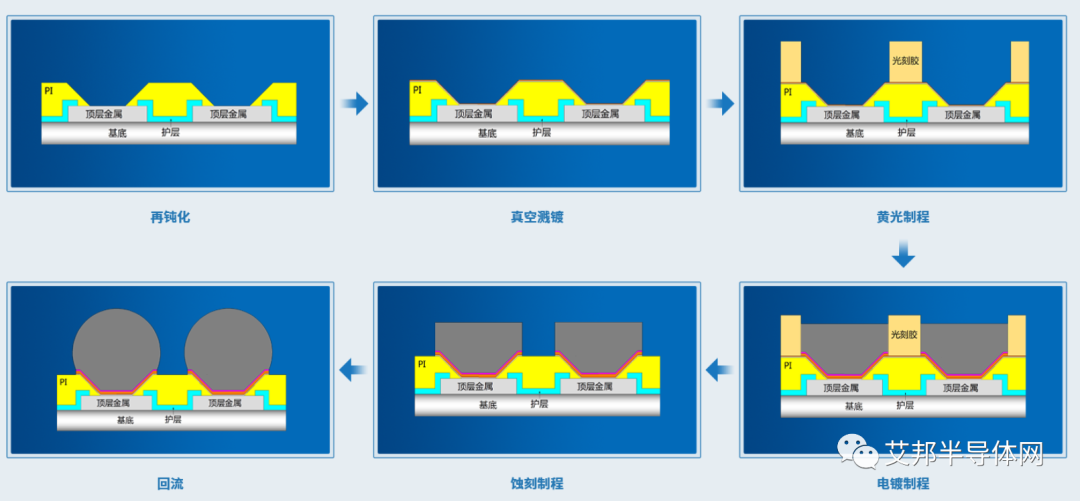

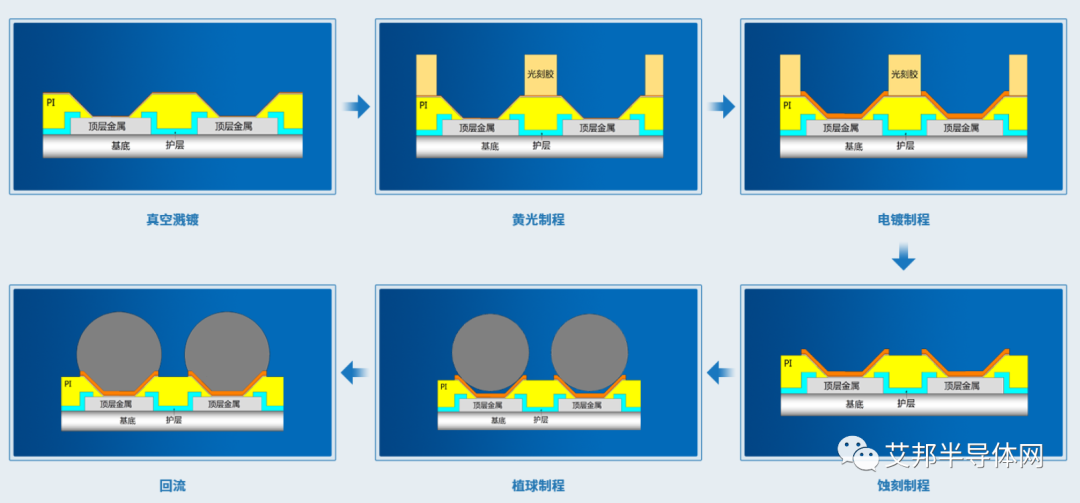

凸塊制(zhì)造技(jì)術(shù)是諸多(duō)先進封裝技(jì)術(shù)得(de)以實現和(hé)進一步發展演化的基礎,經過多(duō)年的發展,凸塊制(zhì)作(zuò)的材質主要有(yǒu)金、銅、銅鎳金、錫等,不同金屬材質适用于不同芯片的封裝,且不同凸塊的特點、涉及的核心技(jì)術(shù)、上(shàng)下遊應用等方面差異較大(dà),具體(tǐ)情況如下:金凸塊,Gold Bumping,是一種利用金凸塊接合替代引線鍵合實現芯片與 基闆之間(jiān)電(diàn)氣互聯的制(zhì)造技(jì)術(shù),主要用于顯示驅動芯片封裝。金凸塊制(zhì)造技(jì)術(shù)主要用于顯示驅動芯片的封裝,少(shǎo)部分用幹傳感器(qì)、電(diàn)子标簽類産品。目前,LCD、AMOLED 等主流顯示面闆的驅動芯片都離不開(kāi)金凸塊制(zhì)造工藝,後續可(kě)通(tōng)過倒裝工藝将芯片倒扣在玻璃基闆(Glass)、柔性屏幕(Plastic)或卷帶(Film)上(shàng),利用熱壓合或者透過導電(diàn)膠材使凸塊與線路上(shàng)的引腳結合起來(lái)。銅鎳金凸塊,CuNiAu Bumping,是一種可(kě)優化 I/O 設計(jì)、大(dà)幅降低(dī)了導通(tōng)電(diàn)阻的凸塊制(zhì)造技(jì)術(shù),凸塊主要由銅、鎳、金三種金屬組成,可(kě)在較低(dī)成本下解決傳統引線鍵合工藝的缺點。在集成電(diàn)路封測領域,銅鎳金凸塊屬于新興先進封裝技(jì)術(shù),近年來(lái)發展較為(wèi)迅速,是對傳統引線鍵合(Wire bonding)封裝方式的優化方案。具體(tǐ)而言,銅鎳金凸塊可(kě)以通(tōng)過大(dà)幅增加芯片表面凸塊的面積,在不改變芯片內(nèi)部原有(yǒu)線路結構的基礎之上(shàng),對原有(yǒu)芯片進行(xíng)重新布線(RDL),大(dà)大(dà)提高(gāo)了引線鍵合的靈活性。此外,銅鎳金凸塊中銅的占比相對較高(gāo),因而具有(yǒu)天然的成本優勢。由于電(diàn)源管理(lǐ)芯片需要具備高(gāo)可(kě)靠、高(gāo)電(diàn)流等特性,且常常需要在高(gāo)溫的環境下使用,而銅鎳金凸塊可(kě)以滿足上(shàng)述要求并大(dà)幅降低(dī)導通(tōng)電(diàn)阻,因此銅鎳金凸塊目前主要應用于電(diàn)源管理(lǐ)類芯片。銅柱凸塊,Cu Pillar,是一種利用銅柱接合替代引線鍵合實現芯片與基闆之間(jiān)電(diàn)氣互聯的制(zhì)造技(jì)術(shù)。銅柱凸塊技(jì)術(shù)是新一代芯片互連技(jì)術(shù),後段适用于倒裝(FC)的封裝形式,應用十分廣泛。銅柱凸塊技(jì)術(shù)是在覆晶封裝芯片的表面制(zhì)作(zuò)焊接凸塊,以代替傳統的打線封 裝,可(kě)以縮短(duǎn)連接電(diàn)路的長度、減小(xiǎo)芯片封裝體(tǐ)積,使其具備較佳的導電(diàn)、導熱和(hé)抗電(diàn)子遷移能力。銅柱凸塊制(zhì)造主要步驟包括再鈍化、真空(kōng)濺鍍、黃光、電(diàn)鍍、蝕刻等,具體(tǐ)工藝流程圖如下:錫凸塊Sn Bumping,是一種利用錫(Sn)接合替代引線鍵合實現芯片與基闆之間(jiān)電(diàn)氣互聯的制(zhì)造技(jì)術(shù)。錫凸塊結構主要由銅焊盤(Cu Pad)和(hé)錫帽(SnAg Cap)構成(一般配合再鈍化和(hé) RDL 層),錫凸塊一般是銅柱凸塊尺寸的 3~5 倍,球體(tǐ)較大(dà),可(kě)焊性更強(也可(kě)以通(tōng)過電(diàn)鍍工藝,即電(diàn)鍍高(gāo)錫柱并回流後形成大(dà)直徑錫球),并可(kě)配合再鈍化和(hé)重布線結構,主要用于 FC 制(zhì)程。錫凸塊技(jì)術(shù)可(kě)以為(wèi)電(diàn)鍍焊錫或植球焊錫,一般情況下,電(diàn)鍍焊錫尺寸可(kě)控制(zhì)的更小(xiǎo)。錫凸塊多(duō)應用于晶圓級芯片尺寸封裝,可(kě)以達到小(xiǎo)尺寸封裝,滿足封裝輕、薄、短(duǎn)、小(xiǎo)的要求。半導體(tǐ)成為(wèi)人(rén)們日常生(shēng)活最重要的組成部分。關注福訊電(diàn)子,為(wèi)您帶來(lái)更多(duō)行(xíng)業前沿咨訊。