晶圓級封裝:适用于移動應用的有(yǒu)吸引力的封裝解決方案

如今,許多(duō)電(diàn)子系統仍然由多(duō)個(gè)元件組成,這些(xiē)元件在晶片切割後單獨封裝,并且使用傳統的印刷電(diàn)路闆互連。然而,這些(xiē)年來(lái),對于更“苛刻”的應用就需要先進的3D集成和(hé)互連技(jì)術(shù)。因為(wèi)這大(dà)大(dà)減小(xiǎo)了電(diàn)子系統的尺寸,并且實現了子電(diàn)路之間(jiān)更快,更短(duǎn)的連接。這些(xiē)技(jì)術(shù)之一是晶圓級封裝(Wafer Level Packaging),即多(duō)個(gè)裸片在晶圓上(shàng)同時(shí)被封裝。由于整個(gè)晶圓現在是一次性封裝,因此該解決方案比傳統封裝方案成本更低(dī)。此外,所得(de)封裝後芯片尺寸更小(xiǎo),更薄,這是智能手機等尺寸敏感設備非常看重的。在現今的智能手機上(shàng),大(dà)概5/7的芯片是晶圓級封裝的,而且數(shù)量還(hái)在不斷增加。

扇入和(hé)扇出

有(yǒu)兩種主要類型的晶圓級封裝:扇入式和(hé)扇出式,它們的區(qū)别主要在重分布層中。重分布層(通(tōng)常是有(yǒu)機層)用于将裸片的接口(I/ O)重新布線到所需的(凸塊)位置。扇入就是重分布層迹線向內(nèi)布線,形成一個(gè)非常小(xiǎo)的封裝(大(dà)緻對應于裸片本身的尺寸)。但(dàn)是,重分布工藝還(hái)可(kě)以用于擴展封裝的可(kě)用區(qū)域,延伸芯片觸點到超出芯片尺寸就形成了扇出式封裝。通(tōng)常,這種扇出WLP(FO-WLP)技(jì)術(shù)提供比扇入式WLP技(jì)術(shù)更多(duō)的I /O數(shù)量。

在移動應用中,扇出晶圓級封裝正在逐步取代更傳統的封裝上(shàng)封裝(PoP)存儲器(qì)邏輯芯片堆疊解決方案。

這些(xiē)PoP比扇出式厚得(de)多(duō),并且受到的互連帶寬和(hé)密度以及有(yǒu)限的間(jiān)距縮放(幾百微米)的限制(zhì)。在這些(xiē)應用中,FO-WLP也優于其他可(kě)用的高(gāo)帶寬3D技(jì)術(shù),例如3D堆疊(其中邏輯管芯中的熱點可(kě)能影(yǐng)響存儲器(qì)數(shù)據保持能力)或2.5D堆疊(其中較長的互連線産生(shēng)較高(gāo)的互連功率和(hé)額外成本)。

兩個(gè)基本的“扇出”流程

在過去幾年中,已經湧現了各種FO-WLP方法,以滿足對高(gāo)數(shù)據速率和(hé)寬I/ O數(shù)量的日益增長的需求,并滿足對封裝上(shàng)增加的功能集成的需求。所有(yǒu)這些(xiē)方法都從兩個(gè)基本的扇出流程中的一個(gè)開(kāi)始:“mold first”或“redistribution layer first”。

在“mold first “工藝中,首先将裸片組裝在臨時(shí)載體(tǐ)上(shàng),然後進行(xíng)晶片包覆成型。環氧樹(shù)脂的功能是保護各個(gè)組件并将它們粘在一起。在最後,制(zhì)作(zuò)重分部層并建立連接。在“redistribution layer first”工藝中,在重分布層的工藝之後再做(zuò)裸片組裝和(hé)晶片注塑成型。

這些(xiē)方法中的每一種都有(yǒu)其自身的一些(xiē)缺點。例如,在“mold first “工藝中,裸片通(tōng)常在注塑成型之後發生(shēng)移位,這使得(de)實現低(dī)于100μm的互連節距非常具有(yǒu)挑戰性。“redistribution layer first”工藝中,可(kě)實現的密度受到(有(yǒu)機)再分布層能夠實現的線和(hé)空(kōng)間(jiān)分辨率的限制(zhì)。

Flip-chip on FO-WLP:一種新的“扇出”方法,可(kě)實現更高(gāo)的互連密度

為(wèi)了滿足更高(gāo)密度,更高(gāo)帶寬的芯片到芯片連接的需求,IMEC團隊在300mm晶圓上(shàng)開(kāi)發了一種新穎的FO-WLP方法,稱為(wèi)Flip-chip on FO-WLP。

這個(gè)工藝屬于“mold first ”工藝,但(dàn)與标準的“mold first ”工藝相反,芯片在包覆成型之前已經互相連接。

下面将解釋這種方法的優點以及挑戰。

關鍵部件:through package vias(TPV)和(hé)矽橋

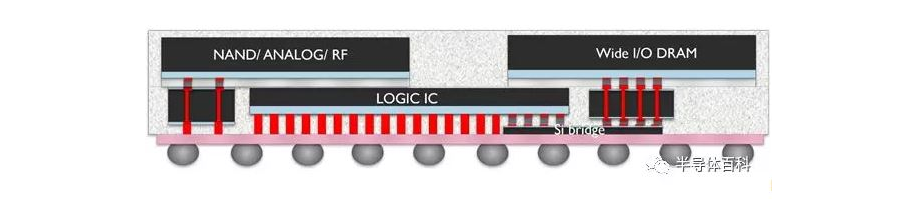

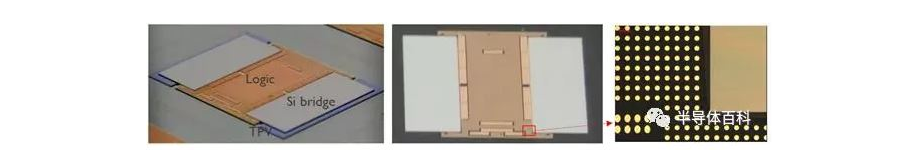

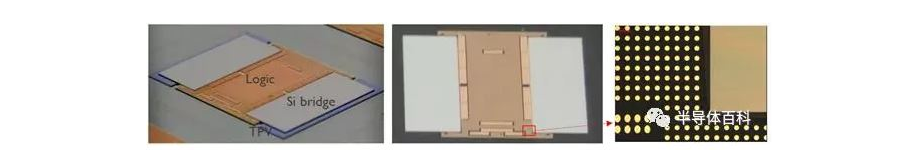

這種新的扇出方案的已經在TQV上(shàng)得(de)到驗證。TQV由七個(gè)獨立的芯片組件組成:Wide I / O DRAM,閃存,邏輯,兩個(gè)TPV裸片和(hé)兩個(gè)矽橋。因為(wèi)這個(gè)TQV隻是用于驗證。因此,邏輯和(hé)存儲器(qì)芯片不是全功能的:它們是“模拟”裸片,用于測試凸點連接之間(jiān)的電(diàn)連續性。

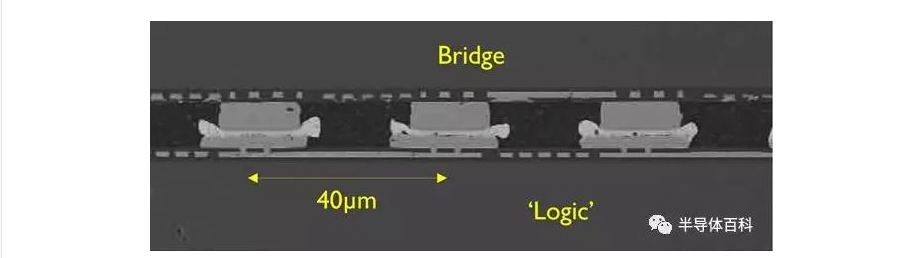

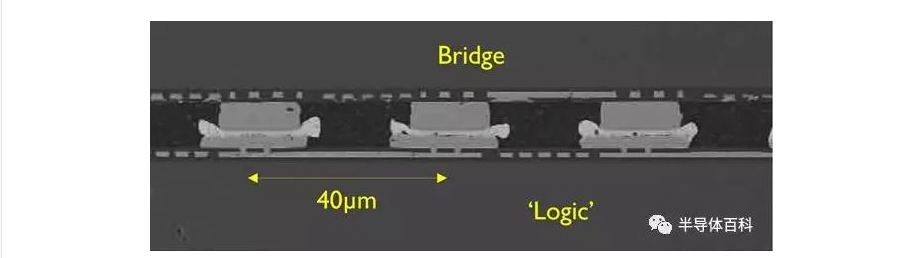

矽橋和(hé)TPV裸片是實現高(gāo)密度連接的關鍵部件。TPV裸片具有(yǒu)矽通(tōng)孔(TSV)和(hé)40μm節距的凸點。矽橋具有(yǒu)40μm和(hé)20μm節距的凸塊。這些(xiē)元件在功能芯片(例如邏輯和(hé)存儲器(qì)芯片)之間(jiān)形成橋接,實現具有(yǒu)20μm凸塊節距的超高(gāo)芯片到芯片互連密度。

與标準“mold first “工藝相比,另一個(gè)關鍵工藝是裸片間(jiān)的緊密對準。在該關鍵組裝步驟中,需要将各個(gè)裸片高(gāo)精度地放置并臨時(shí)鍵合在平坦的矽晶圓上(shàng)。

Flip-chip19081301.JPGFlip-chip on FO-WLP芯片概念圖。

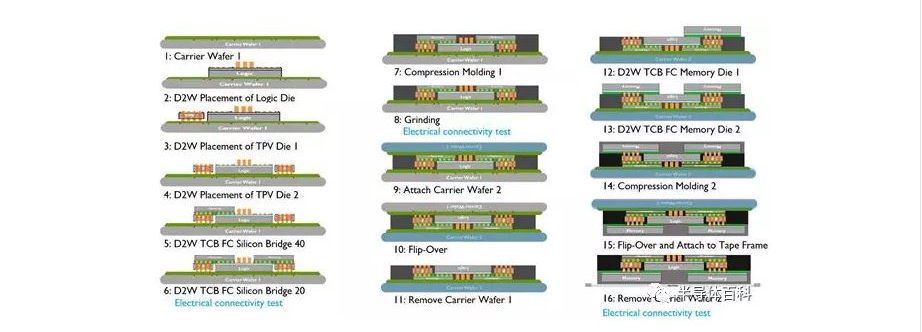

工藝流程細節

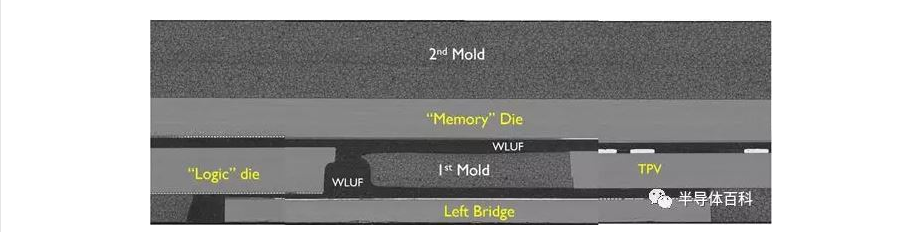

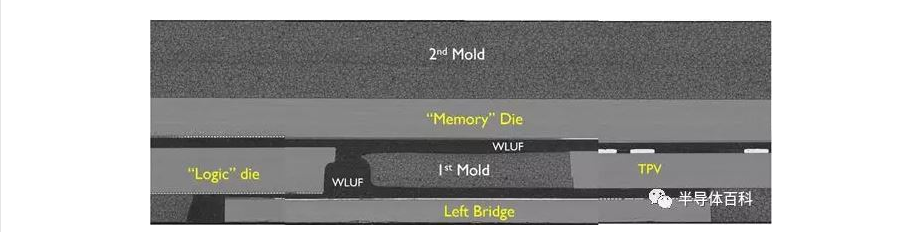

在組裝工藝流程的第一步驟中,将TPV片和(hé)邏輯裸片放置在覆有(yǒu)臨時(shí)鍵合層的載體(tǐ)晶片上(shàng)。接下來(lái),使用熱壓接合(TCB)工藝連接矽橋(具有(yǒu)40μm和(hé)20μm的凸塊間(jiān)距)與邏輯裸片和(hé)TPV裸片。在該工藝步驟中,具有(yǒu)40μm節距的凸塊連接到邏輯裸片的左側和(hé)TPV裸片。20μm間(jiān)距凸塊連接到邏輯裸片的右側。在下一步驟中,晶片由液态化合物注塑成型。測試顯示完全填充,甚至是矽橋下方區(qū)域。然後,通(tōng)過研磨抛光暴露銅柱,以便稍後與重分布層連接。在将減薄的晶片翻轉并第二載體(tǐ)鍵合,并移除第一載體(tǐ)。之後,使用倒裝芯片技(jì)術(shù)組裝存儲器(qì)裸片。最後,再一次晶圓級注模和(hé)第二載體(tǐ)的移除完成工藝流程。在工藝步驟之間(jiān),會(huì)進行(xíng)連續性測試以驗證電(diàn)路完整。最後得(de)到封裝厚度僅為(wèi)300-400μm的芯片(不包括焊球)。

Flip-chip19081302.JPGFlip-chip on FO-WLP芯片:封裝工藝流程

Flip-chip19081303.JPG圖示了裸片放置和(hé)橋接之後的步驟5至8(左); 在注塑和(hé)背面研磨之後(中)和(hé)暴露的Cu柱在封裝體(tǐ)表面上(shàng)(右)

Flip-chip19081304.JPG最終的第二晶圓級成型之後的橫截面

主要挑戰和(hé)解決方案

這套工藝流程帶來(lái)了一系列挑戰,需要克服這些(xiē)挑戰才能确保具有(yǒu)超高(gāo)芯片到芯片互連密度的全功能封裝解決方案。

其中一個(gè)問題是在組裝工藝流程中裸片可(kě)能傾斜,特别是對于長而窄的TPV裸片和(hé)矽橋。這些(xiē)裸片的傾斜可(kě)能會(huì)破壞組件之間(jiān)的互連。為(wèi)了評估傾斜是否以及何時(shí)發生(shēng),IMEC團隊采用不同的力量來(lái)放置TPV裸片。該團隊觀察到,即使是最大(dà)的貼裝力,傾斜也限制(zhì)在5μm以下,這足夠低(dī)以保持連接性。

接下來(lái)是,邏輯裸片和(hé)TPV裸片之間(jiān)的對準,這已經引起了相當大(dà)的關注,并且被認為(wèi)是FO-WLP工藝的關鍵因素。

邏輯裸片和(hé)TPV裸片彼此靠的非常近,并且需要精确的對準步驟以實現後續的矽橋40μm和(hé)20μm凸塊節距堆疊。例如,為(wèi)了實現所需的20μm凸塊間(jiān)距,僅可(kě)以容忍邏輯裸片和(hé)TPV裸片之間(jiān)的最大(dà)+/-3μm的對準誤差。為(wèi)了實現這種極小(xiǎo)的誤差,該團隊将對準标記引入到載體(tǐ)和(hé)裸片設計(jì)中。邏輯裸片首先與載體(tǐ)對準。接下來(lái),放置TPV裸片,與載體(tǐ)對準因此與邏輯管芯對準。最後,使用高(gāo)精度堆疊熱壓鍵合設備來(lái)放置矽橋。

Flip-chip19081305.JPG矽橋連接鍵合到邏輯裸片上(shàng)的示例

在随後的模制(zhì)過程中,裸片仍然會(huì)移位,從而損壞TPV和(hé)矽橋之間(jiān)或邏輯裸片和(hé)矽橋之間(jiān)的凸塊連接。因此,IMEC團隊在成型之前和(hé)之後進行(xíng)了專門(mén)的電(diàn)氣測試。測試表明(míng),模塑過程不會(huì)影(yǐng)響連接的完整性。基于這些(xiē)結果,可(kě)以假設,如果這些(xiē)裸片在注塑時(shí)移位,它們應該是在相同的方向上(shàng)作(zuò)整體(tǐ)位移,因而不會(huì)破壞連接性。

總結和(hé)未來(lái)展望

通(tōng)過這種新穎的方法,IMEC團隊在扇出環境中展示了具有(yǒu)20μm凸塊節距的創紀錄的芯片到芯片互連密度。在不久的将來(lái),該技(jì)術(shù)将得(de)到進一步改進,電(diàn)氣和(hé)射頻行(xíng)為(wèi)将以不同的配置進行(xíng)評估。

所提出的技(jì)術(shù)對于移動應用尤其具有(yǒu)吸引力,因為(wèi)它以非常小(xiǎo)的形狀因子實現了經濟有(yǒu)效的WideI / O存儲器(qì)到邏輯芯片互連。

最終,FO-WLP上(shàng)的倒裝芯片也可(kě)能成為(wèi)異構集成的支持技(jì)術(shù),瞄準高(gāo)性能應用。它可(kě)以提供一種在電(diàn)氣高(gāo)度互連的封裝中集成多(duō)個(gè)裸片的方法,包括高(gāo)性能計(jì)算(suàn),存儲器(qì)和(hé)光通(tōng)信模塊。